IMB-CNM develops a specific phase-locked loop circuit for the new Sargantana chip

Sargantana, the new generation of open source chips based on advanced RISC-V processors, was presented by the Barcelona Supercomputing Center on Wednesday, December 20, in the framework of the DRAC project. As in previous releases, IMB-CNM has collaborated in a critical part of the development.

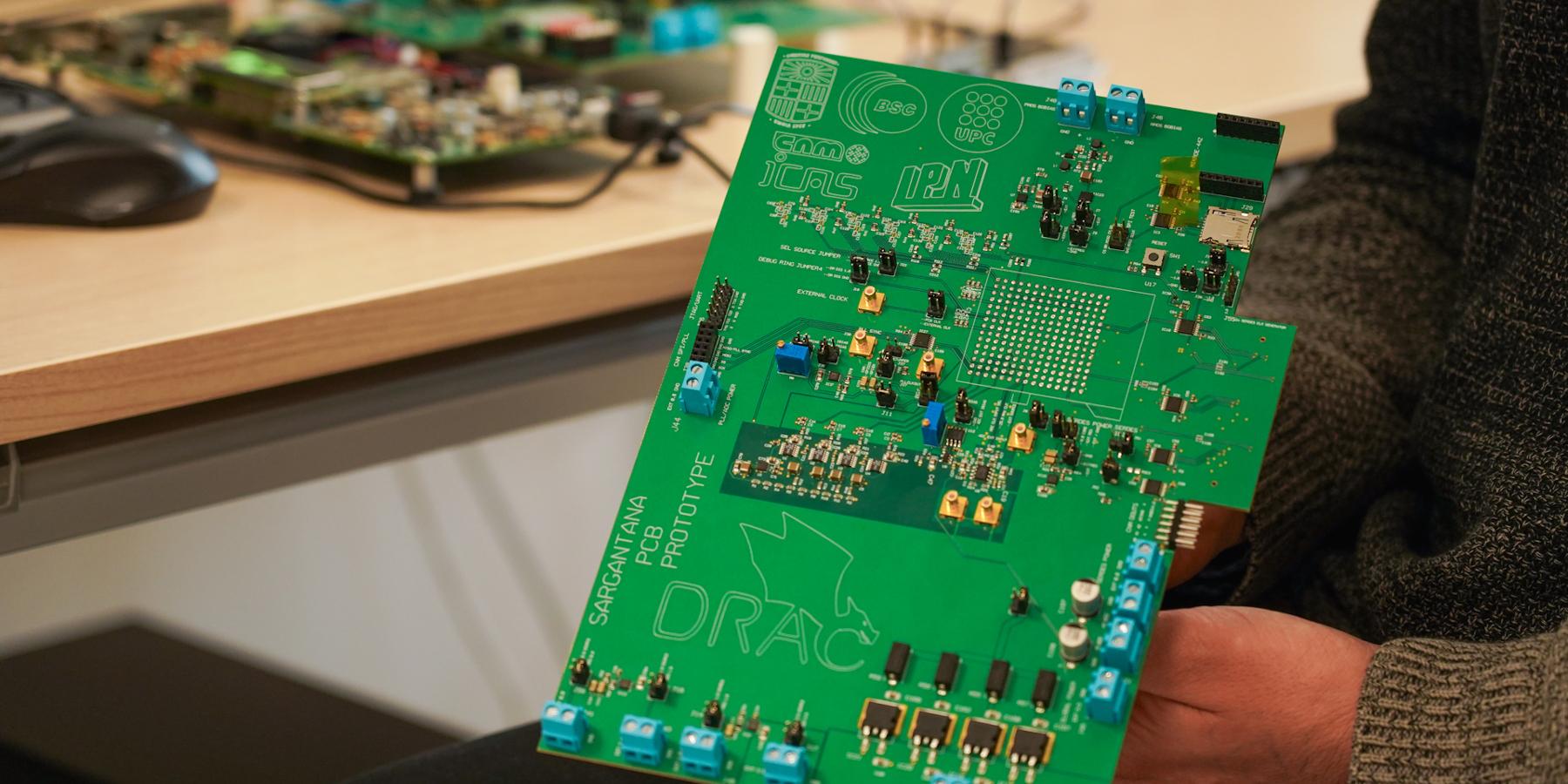

The Institute of Microelectronics of Barcelona (IMB-CNM-CSIC) has developed a specific phase-locked loop (PLL) circuit for the new advanced RISC-V processors of the DRAC project led by the Barcelona Supercomputing Center - Centro Nacional de Supercomputación (BSC-CNS). The BSC-CNS presented last December 20 the new Sargantana chip, the third generation of open source processors.

Sargantana (name of lizard in Aragonese and Catalan) is the third generation of the Lagarto processors, the first open source chips developed in Spain, within the framework of the DRAC project (Designing RISC-V-based Accelerators for next generation Computers), and is one of the most advanced open source chips in Europe at an academic level. The new Sargantana features better performance delivery than its two predecessors - Lagarto Hun (2019) and DVINO (2021) - and is the first processor in the Lagarto family to break the gigahertz barrier in operating frequency.

While the RISC-V is the brain of the processor, the PLL developed by IMB-CNM-CSIC is the heart of the processor, as it is the circuit in charge of setting its operating rate. Thanks to new technologies, it is possible to make the cores of the chips work at much higher rates than the external signals of the printed circuit boards where they are assembled. "This makes it possible to obtain better performance and offer 10 to 20 times higher yields than the circuits that manage computers outside the processor, but it requires a PLL that allows the execution rate of the instructions to be increased," explains Lluís Terés, a researcher in the Integrated Circuits and Systems group (ICAS).

The design of the IMB-CNM-CSIC PLL uses an external reference frequency of 100 MHz to generate an internal clock, digitally programmable and synchronized, from 1.2 GHz to 2.4 GHz, which can be extended up to 3 GHz. In fact, this PLL directly generates working frequency combinations of N/R times 100 MHz, where N and R are whole numbers. This makes it possible to offer a wide range of operating rates to the processor, which will be able to adapt the execution speed to the workloads and thus optimize its power consumption. The developed circuit has been integrated on the same chip as the RISC-V Sargantana core of the BSC with 22 nm CMOS technology from Global Foundries, with the PLL block occupying an area of only 0.0064 mm².

While the RISC-V is the brain of the processor, the PLL developed by the IMB-CNM-CSIC is the heart of the processor, since it is the circuit in charge of setting its operating rhythm. Thanks to new technologies, it is possible to make the cores of the chips work at much higher rates than the external signals of the printed circuit boards where they are assembled.

Coordinated joint work in the DRAC project

In the development of Sargantana, a project coordinated by the BSC-CNS, research personnel from other universities and research centers, beyond the IMB-CNM-CSIC, have participated, such as the Centro de Investigación en Computación del Instituto Politécnico Nacional de México (CIC-IPN), the Universitat Politècnica de Catalunya (UPC), the Universitat Autònoma de Barcelona (UAB), the Universitat de Barcelona (UB) and the Universitat Rovira i Virgili (URV).